|

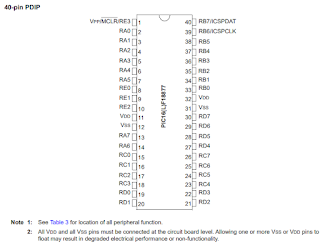

| PIC16F18877 |

|

| Imagen de Microchip Technologhy Inc |

Interrupciones

La función de interrupción permite que ciertos eventos se anticipen

Flujo normal del programa. El firmware se utiliza para determinar

la fuente de la interrupción y actuar en consecuencia. Alguno

las interrupciones se pueden configurar para reactivar el MCU desde

Modo de suspensión.

Este capítulo contiene la siguiente información para

Interrupciones:

Operación, Latencia de interrupción, interrupción durante el sueño, INT PIN,

Operación:

Las interrupciones se desactivan en cualquier restablecimiento del dispositivo. Ellos

se habilitan estableciendo los siguientes bits:

- GIE BIT del registro INTCON

- PEIE bit del registro INTCON

Los registros PIR1, PIR2, PIR3 y PIR4 registran

Interrupciones individuales a través de bits de indicador de interrupción. Indicador de interrupción

se establecerán bits, independientemente del estado del GIE, PEIE

y bits de habilitación de interrupción individual.

Interrupt Latency:

La latencia de interrupción se define como el tiempo transcurrido desde el momento en que el

Se produce un evento de interrupción en la ejecución del código de tiempo en el directorio

Comienza el vector de interrupción. La latencia para sincrónico

Interrupciones son tres o cuatro ciclos de instrucción. Para

Interrupciones asíncronas, la latencia es de tres a cinco

ciclos de instrucción, dependiendo de cuándo se interrumpe

Ocurre.

Interrupts During Sleep:

Algunas interrupciones se pueden usar para despertarse del sueño. Para

despertar de la suspensión, el periférico debe ser capaz de

Operar sin el reloj del sistema. El origen de la interrupción

debe tener los bits de habilitación de interrupción adecuados

antes de entrar en reposo.

Al despertar del modo de suspensión, si también se establece el bit GIE, el

El procesador se ramificará al vector de interrupción. De otra manera

El procesador continuará ejecutando instrucciones después

la instrucción SLEEP. La instrucción directamente después de la

La instrucción SLEEP siempre se ejecutará antes

ramificación al ISR.

INT PIN

El pin INT se puede utilizar para generar un pin asíncrono

Interrupción activada por borde. Esta interrupción está habilitada por

estableciendo el bit INTE del registro PIE0. El bit INTEDG

del registro INTCON determina en qué arista el

Se producirá una interrupción. Cuando se establece el bit INTEDG, el

Rising Edge causará la interrupción. Cuando el INTEDG

bit es claro, el borde de caída causará la interrupción. El

El bit INTF del registro PIR0 se establecerá cuando un

edge aparece en el pin INT. Si los bits GIE e INTE

también están configurados, el procesador redirigirá el programa

Ejecución al vector de interrupción.

Módulo TIMER0

El módulo Timer0 es un temporizador/contador de 8/16 bits con el

Características siguientes:

• 16-bit timer/counter

• 8-bit timer/counter with programmable period

• Synchronous or asynchronous operation

• Selectable clock sources

• Programmable prescaler (independent of

Watchdog Timer)

• Programmable postscaler

• Operation during Sleep mode

• Interrupt on match or overflow

• Output on I/O pin (via PPS) or to other peripherals

TIMER0 Operation

Timer0 puede funcionar como un temporizador/contador de 8 bits o

Un temporizador/contador de 16 bits. El modo se selecciona con el botón

Bit T016BIT del registro T0CON.

Cuando se utiliza con una fuente de reloj interna, el módulo es

un temporizador e incrementos en cada ciclo de instrucción.

Cuando se utiliza con una fuente de reloj externa, el módulo

se puede utilizar como temporizador o contador y

incrementos en cada borde ascendente de la fuente externa.

16 BIT MODE

En funcionamiento normal, TMR0 se incrementa en el aumento

borde de la fuente del reloj. Un escalador previo de 15 bits en el

La entrada de reloj ofrece varias opciones de preescala (consulte

bits de control del preescalador, T0CKPS<3:0> en el T0CON1

registrarse).

TIMER0 LEE Y ESCRIBE EN 16 BITS

TMR0H no es el byte alto real de Timer0 en 16 bits

modo. En realidad, es una versión en búfer del subidón real

byte de Timer0, que no es legible directamente ni

Escritura. TMR0H se actualiza con el

contenido del byte alto de Timer0 durante una lectura de

TMR0L. Esto proporciona la capacidad de leer los 16 bits de

Timer0 sin tener que verificar que la lectura del alto

y el byte bajo era válido, debido a un rollover entre

lecturas sucesivas del byte alto y bajo.

Del mismo modo, una escritura en el byte alto de Timer0 también debe

tienen lugar a través del registro TMR0H Buffer. El alto

byte se actualiza con el contenido de TMR0H cuando un

la escritura se produce en TMR0L. Esto permite que los 16 bits de Timer0

para ser actualizado de inmediato.

MODO 8 BIT

En funcionamiento normal, TMR0 se incrementa en el aumento

borde de la fuente del reloj. Un escalador previo de 15 bits en el

La entrada de reloj ofrece varias opciones de preescala (consulte

bits de control del preescalador, T0CKPS<3:0> en el T0CON1

registrarse). El valor de TMR0L se compara con el del período

buffer, una copia de TMR0H, en cada ciclo de reloj. Cuando

Los dos valores coinciden, ocurren los siguientes eventos:

• TMR0_out sube alto para un reloj preescalado

periodo

• TMR0L se restablece

• Los contenidos de TMR0H se copian al período

Buffe

En el modo de 8 bits, los registros TMR0L y TMR0H son

ambos directamente legibles y escribibles. El TMR0L

el registro se borra en cualquier dispositivo Restablecer, mientras que el

El registro TMR0H se inicializa en FFh.

Los contadores de preescalador y postescalador se borran

en los siguientes eventos:

• Una escritura en el registro TMR0L

• Una escritura en T0CON0 o T0CON1

Registros

• Restablecimiento de cualquier dispositivo: restablecimiento de encendido (POR),

Restablecimiento de MCLR, restablecimiento del temporizador de vigilancia (WDTR) o

• Brown-out Reset (BOR)

MODO CONTADOR

Cuando se establece el bit T0ASYNC del registro T0CON1

(T0ASYNC = '1'), el contador se incrementa con cada

borde ascendente de la fuente de entrada (o salida de la

preescalador, si se utiliza). El modo asíncrono permite la

contador para continuar el funcionamiento durante el modo de suspensión

siempre que el reloj también continúe funcionando durante

Dormir.

MODO SÍNCRONO

Cuando el bit T0ASYNC del registro T0CON1 está claro

(T0ASYNC = 0), el reloj del contador está sincronizado con

el oscilador del sistema (FOSC/4). Cuando se opera en

Modo síncrono, la frecuencia del reloj del contador

no puede exceder FOSC/4.

SELECCION DE FUENTE DE RELOJ

Se utilizan los bits T0CS<2:0> del registro T0CON1

para seleccionar la fuente del reloj para Timer0. Registro 27-2

Muestra las selecciones de origen del reloj.

RELOJ INTERNO.

Cuando se selecciona la fuente del reloj interno, Timer0

funciona como un temporizador y se incrementará en múltiplos de

la fuente del reloj, según lo determinado por el temporizador0

preescalador.

RELOJ EXTERNO:

Cuando se selecciona una fuente de reloj externa, Timer0 puede

Opere como un temporizador o un contador. Timer0 will

Incremento en múltiplos del borde ascendente del externo

fuente de reloj, según lo determinado por el escalador previo Timer0.

PREESCALADOR:

Un preescalador programable por software está disponible para

uso exclusivo con Timer0. Hay 16 preescaladores

opciones para Timer0 que varían en potencias de dos de 1:1 a

1:32768. Los valores del preescalador se seleccionan mediante el comando

T0CKPS<3:0> bits del registro T0CON1.

El escalador previo no es directamente legible ni escribible.

La limpieza del registro del preescalador se puede hacer escribiendo

al registro TMR0L o al registro T0CON1.

POSTCALADOR:

Un postescalador programable por software (divisor de salida) es

disponible para uso exclusivo con Timer0. Hay 16

opciones de postscaler para Timer0 que van de 1:1 a 1:16.

Los valores del postescalador se seleccionan mediante el comando

T0OUTPS<3:0> bits del registro T0CON0.

El postescalador no es directamente legible ni escribible.

La limpieza del registro postscaler se puede hacer escribiendo

al registro TMR0L o al registro T0CON0.

INTERRUPCION TIMER0:

El bit de indicador de interrupción Timer0 (TMR0IF) se establece cuando

Se produce cualquiera de las condiciones siguientes:

• TMR0L de 8 bits coincide con el valor TMR0H

• TMR0 de 16 bits se transfiere de 'FFFFh'

Cuando los bits del postescalador (T0OUTPS<3:0>) se establecen en

Operación 1:1 (sin división), se establecerá el bit de indicador T0IF

con cada coincidencia o rollover TMR0. En general, el

El bit de indicador TMR0IF se establecerá cada T0OUTPS +1 coincidencias

o vuelcos.

Sí las interrupciones Timer0 están habilitadas (bit TMR0IE del

Registro PIE0 = 1), la CPU se interrumpirá y el

El dispositivo puede despertarse del modo de suspensión.

La salida Timer0 se puede enrutar a cualquier pin de E/S a través del

Registro de selección de salida RxyPPS.

La salida Timer0 también puede ser utilizada por

otros periféricos, como el disparador de conversión automática

del convertidor analógico a digital. Finalmente, el Timer0

La salida se puede monitorear a través del software a través del

Bit de salida Timer0 (T0OUT) del registro T0CON0.

TMR0_out será un período de reloj postescalado cuando un

Se produce una coincidencia entre TMR0L y TMR0H en 8 bits

o cuando TMR0 se transfiere en modo de 16 bits. El

La salida Timer0 es un ciclo de trabajo del 50% que activa cada

TMR0_out borde creciente del reloj.

Sí lo vas a simular en proteus, solo es compatible con versiones superiores a la 8.14

Comentarios

Publicar un comentario